Micron und Samsung liefern sich ein Speicher-Wettrennen

Micron hat die Serienproduktion von HBM3e-RAM verkündet, Samsung folgt. Nvidia ist der erste Abnehmer mit seinen H200-GPUs.

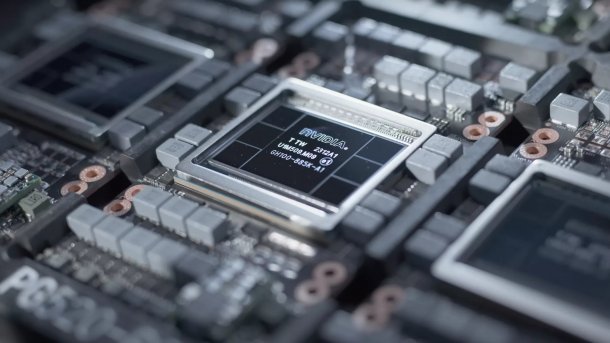

Nvidias Hopper-GPU verwendet bisher sechs HBM3-Bausteine, kommt als H200 aber auch mit HBM3e.

(Bild: Nvidia)

Micron und Samsung liefern sich ein Wettrennen bei der Markteinführung von High-Bandwidth Memory der Generation HBM3e, auf die unter anderem AMD und Nvidia warten. Micron hat laut eigener Ankündigung mit der Serienproduktion von HBM3e-Bausteinen begonnen, die 24 GByte fassen und bei Maximalgeschwindigkeit rund 1,2 TByte/s übertragen.

Nvidia setzt den Micron-Speicher bei seinem H100-Refresh H200 ein. Bisher gibt es die H100 nur mit 80 GByte HBM3 beziehungsweise bei der NVL mit 94 GByte HBM3. Bei letzterer ist auch der sechste Baustein aktiv, allerdings deaktiviert Nvidia für eine bessere Ausbeute manche Speicherlagen. Die H200 stellt so krumme 141 GByte HBM3e bereit. Nvidia reizt den Maximaltakt allerdings nicht aus; die Gesamt-Übertragungsrate steigt auf 4,8 TByte/s (H100: 3,35 TByte/s, H100 NVL: 3,9 TByt/s).

36-GByte-Stapel kommen

Ab März 2024 will Micron HBM3e-Muster an Partner schicken, die 12 statt 8 Speicherlagen und somit 36 statt 24 GByte Kapazität haben. Konkurrent Samsung will Micron zuvorkommen und hat laut eigener Ankündigung bereits mit der Bemusterung sogenannter 12-Hi-Bausteine begonnen. Jeder HBM3e-Stapel überträgt 1,28 TByte/s. Die Firma springt offenbar direkt auf 36-GByte-Varianten und legt keine 24-GByte-Versionen auf – solche bietet Samsung schon in Form langsamerer HBM3-Stapel an.

Laut Samsung sind die 36-GByte-Bausteine genauso hoch wie die 24er, sodass die neuen Chips auf bisherige Prozessoren und Beschleuniger passen. Dazu wurden die Speicherlagen ausgedünnt und die Zwischenräume verkleinert. Bis zur Jahresmitte soll die Serienproduktion anlaufen.

MI300 künftig mit 288 GByte RAM

Ein potenzieller Abnehmer ist AMD mit seinen MI300-Beschleunigern. Sie verwenden bisher acht HBM3-Stacks, die es auf eine Kapazität von 192 GByte und eine Übertragungsrate von 5,2 TByte/s bringen. Mit einem Upgrade wären 288 GByte und an die 10 TByte/s drin, wovon insbesondere große KI-Modelle profitieren könnten.

Auf einer Konferenz ließ AMDs Technikchef Mark Papermaster verlauten, dass die MI300 bereits für HBM3e mit 12 Speicherlagen vorbereitet sei (Transkript bei Seeking Alpha). AMD habe die eigene Roadmap vorgezogen, unter anderem mit neuen Speicherkonfigurationen.

Lesen Sie auch

Die MI300 ist AMDs Hoffnungsträger für das Jahr 2024

Vermutlich kein HBM mehr für GeForce- und Radeon-Grafikkarten

HBM3e und nachfolgende Generationen bleiben derweil mit hoher Wahrscheinlichkeit Profi-Hardware vorbehalten, also primär Serverbeschleunigern. Raja Koduri, früher Chefingenieur bei AMD und Intel, hält die Kosten von HBM für Spiele-Grafikkarten zu hoch. Zum einen sind die Bausteine selbst teuer, zum anderen ist das Zusammensetzen (Packaging) aufwendig.

Unter Koduri hat AMD vor Jahren noch die einzigen Spiele-Grafikkarten mit HBM gebracht: zuerst die Radeon R9 Fury X und R9 Fury, später die Radeon RX Vega 64, RX Vega 56 und Radeon VII. Inzwischen ist AMD aber auf günstigeren GDDR6-Speicher bei seinen Radeons umgeschwenkt.

Neue GDDR-Generationen steigern die Geschwindigkeit mit höheren Taktfrequenzen und komplexerer Pulsamplitudenmodulation, mit der sich mehr Zustände pro Takt auslesen lassen. HBM geht dagegen in die Breite: Bisher ist ein Baustein über 1024 Datenleitungen angebunden, HBM4 wechselt auf 2048 Bit pro Baustein.

(mma)