Neuromorphe Chips für neuronale Netze

Künstlich gelernt

Sollten neuronale Netzwerke noch größere Verbreitung erfahren, ist herkömmliche Hardware nicht effizient genug. Neuromorphe Chips versprechen, durch Spezialisierung und analoges Rechnen weniger Energie zu verbrauchen.

Ein neues Bauteil schleicht sich neben CPU und GPU auf den Markt: die NPU, kurz für Neuromorphic Processing Unit, neuromorpher Prozessor – oft auch als neurosynaptischer oder neuraler Prozessor bezeichnet. Die NPU soll die Arbeit mit neuronalen Netzen erleichtern. Diese Spielart der künstlichen Intelligenz ist hervorragend in der Gestalt- und Mustererkennung und kann Merkmale mit hoher Geschwindigkeit extrahieren, was sie zur Analyse großer Datenmengen empfiehlt. Die akademischen Erfolge aus den 80er-Jahren fanden damals jedoch keine Fortführung in der Industrie.

Jüngst wächst allerdings das Interesse daran spürbar, denn es gibt neue Aufgaben, etwa bei autonom gesteuerten Autos, Schiffen und Flugzeugen oder bei der Sprach- und Mustererkennung. Klassische Rechner mit Von-Neumann-Architektur, die sequenziell ihre Aufgaben abarbeiten, sind zu ressourcenhungrig hierfür. Das trifft vor allem im mobilen Bereich zu, letztlich aber auch im Rechenzentrumsmaßstab, denn wenn immer mehr Menschen Sprachassistenten wie Alexa oder Googles Bildrecherche verwenden, würden diese Dienste für die Anbieter zu teuer.

Auf klassischen Computern

In den 40er-Jahren des letzten Jahrhunderts dachten die ersten Pioniere über selbstlernende Rechner nach (siehe Kasten „Anfänge der künstlichen Intelligenz“). Die erste Blüte der künstlichen Intelligenz datiert auf die 80er-Jahre, als neuronale Netze erstmals erfolgreich auf klassischen Computern implementiert wurden. Sie konnten einfache Aufgaben lösen, ohne dass ein Programm erstellt werden musste.

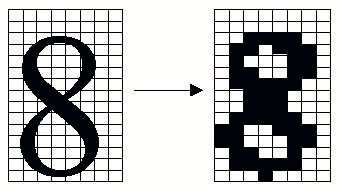

Neuronale Netze sind ein simples Modell der Vorgänge im menschlichen Gehirn. Sie bestehen aus Eingabeneuronen, einer oder mehreren Schichten Rechenneuronen und Ausgabeneuronen (siehe Abbildung 2). Je mehr Ebenen zwischen Ein- und Ausgabe liegen, desto höher ist die Präzision, aber auch der Rechenaufwand. Erfolgreich waren die neuronalen Netze damals nur im akademischen Umfeld. Bei einfachen Aufgaben in der Mess- und Regeltechnik konnten sie sich auf den preiswerten CPUs nicht gegen konventionelle Algorithmen durchsetzen. Bei schwierigen Aufgaben wurden die Anforderungen an die Hardware zu hoch. „Tiefe“ neuronale Netze mit vielen hintereinandergeschalteten Neuronen verschlangen so viel Rechenleistung, dass diese Lösungen finanziell unattraktiv blieben.

Die damaligen Rechner arbeiteten wie alle Von-Neumann-Rechner sequenziell und trennten strikt zwischen Datenverarbeitung und Speicher. Im Gehirn ist beides eine untrennbare Einheit und zudem räumlich eng verschaltet. Eine neue Generation von Forschern begann im ersten Jahrzehnt des 21. Jahrhunderts, die leistungsfähige Rechentechnik unserer Zeit zu nutzen und gleichzeitig auf die Marktanforderungen zu reagieren (siehe Artikel „Nichts verallgemeinern“ auf Seite 46). Sie verwendeten Grafikprozessoren, um neuronale Netze beispielsweise zur Muster- und Spracherkennung zu berechnen. In allen Fällen lernt das Netz aus unzähligen Beispielen jene Regeln, die es später anwenden soll. Schon diese großen Datenmengen hätte es in den 80er-Jahren nicht gegeben, heute sind die Archive und Datenbanken voll davon.

Absolutes Neuland für die IT

Vor allem in den USA begann man frühzeitig, neue Wege bei der Hardware zu gehen. Dafür sollten Chips entstehen, die dem menschlichen Gehirn so weit wie möglich entsprechen, inklusive der neuronalen Plastizität. Das ist die Eigenart von Synapsen, sich zur Optimierung in ihrer Struktur hardwaremäßig zu verändern. Der Chip würde quasi anfangen zu leben, auch wenn dies nur die elektrischen Eigenschaften seiner Komponenten beträfe. Er wäre nach der Lernphase ein anderer Chip, der sich nicht ohne Weiteres in den Ursprungszustand zurückversetzen ließe. Man spricht von neuromorphen Architekturen.

Trotzdem sollen diese Rechner Turing-vollständig und damit universell programmierbar sein. Turing-Maschinen sind sie jedoch nicht. Forschungsarbeiten am Institut für Neuroinformatik der Universität Zürich weisen allerdings darauf hin, dass sich Turing-Maschinen auf ihnen simulieren lassen. Einer der ersten großtechnisch gefertigten neuromorphen Chips mit Non-von-Neumann-Architektur ist der TrueNorth-Chip von IBM – wenn man ihn überhaupt schon so bezeichnen darf. Die Firma kündigte ihn 2014 als Chip mit „neuromorpher“ Architektur an – ähnlich dem menschlichen Gehirn [1].

Erst zwei Jahre später gelang es, die für effizientes Lernen wichtige Backpropagation für das Offline-Learning zu implementieren – schon früh hat sich diese mathematische Methode etabliert, um neuronale Netze zu trainieren. Voraussetzung ist etwas wie ein externer Lehrer, der als Maßstab für Korrekturen dient. Die Ausgabe des Netzes wird mit dem gewünschten Ergebnis verglichen. Die Differenz der beiden Werte wird als Fehler des Netzes erachtet. Daraus resultiert eine Veränderung der Gewichtungen innerhalb der Neuronenverbindungen. Mit jedem weiteren Schritt nähert sich das Ergebnis dem korrekten Wert an.

IBM wählte das Elitemagazin der Grundlagenforschung, „Science“, um den Prozessor vorzustellen. Ein deutlicher Hinweis, dass neuromorphe Chips die Sphäre der Grundlagenforschung noch nicht gänzlich verlassen haben. TrueNorth entstammt dem 2005 gestarteten Programm SyNAPSE (Systems of Neuromorphic Adaptive Plastic Scalable Electronics) der Forschungseinrichtung Darpa des US-Militärs.